W kolejnym artykule na portalu iAutomatyka.pl postanowiłem opisać sposób w jaki zasymulowałem układ regulatora PID w środowisku Codesys. Był to jeden z etapów realizacji mojej pracy magisterskiej. Podstawy regulatora PID (proporcjonalno-całkująco-różniczkujący) zna każdy automatyk, jednak jak zrealizować teorię podawaną na studiach oraz symulację wykonaną w Matlab-ie na rzeczywistym sterowniku? Nie jest to już takie łatwe. Pełny kurs można znaleźć na stronie portalu: iAUTOMATYKA kurs PID. Kurs dostepny jest też bezpłatnie na platformie KursyAutomatyki.pl – LINK: https://kursyautomatyki.pl/kurs/kurs-regulacji-pid/

W moim przypadku, wykorzystałem symulator sterownika w środowisku Codesys v3.5. Dotychczas nie miałem doświadczenia w programowaniu w tym programie, dlatego postanowiłem wykorzystać to jako okazję do zdobycia nowych umiejętności.

W omawianym poniżej przykładzie użyłem poniższego układu regulacji (układ regulacji PID sterujący obiektem inercyjnym I-rzędu z różną skalą wartości opóźnienia transportowego do stałej inercji obiektu). W pracy wykorzystałem regulator PID z układem AWC (anti-windup compensator) oraz ograniczeniem sygnału sterującego.

Na początku podzieliłem program sterownika na 3 części:

- Sygnał zadany – odpowiada za generowanie przebiegu sygnału zadanego w języku LAD.

- Regulator PID z układem AWC – blok przeliczania wartości regulatora napisany w języku ST.

- Model obiektu – blok przeliczania wyjścia obiektu w języku ST.

Generowanie sygnału zadanego

Na potrzeby testu był to sygnał prostokątny zrealizowany na dwóch blokach move oraz timerze. Timer po osiągnięciu wartości PT jest resetowany poprzez zmianę stanu zmiennej „Timer” (zmienna „START_TUNE” służy do uruchomienia symulacji). W drugiej linii w zależności od wartości zmiennej bloku „LT” zmieniamy czas trwania stanu niskiego „0” i wysokiego „1”.

Regulator PID

Mając sprawdzony blok regulatora PID w programie Matlab przystąpiłem do przygotowania bloku regulatora w programie Codesys. Poniżej umieściłem kod regulatora PID w języku ST. W bloku zostały wyliczone wartości każdego z członów regulatora, ograniczenie sygnału sterującego przy użyciu pętli warunkowych IF oraz części kompensacyjnej (dodawana w członie całkującym). Wyliczenie uchybu odbywa się na podstawie różnicy zmiennych, gdzie przechowywana jest wartość zadana oraz wyjścia z obiektu.

Blok obiektu

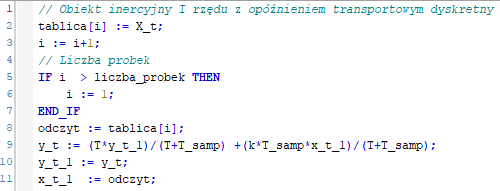

Do pierwszej weryfikacji układu wykorzystałem przygotowany program obiektu inercyjnego pierwszego rzędu z opóźnieniem transportowym. Opóźnienie transportowe zostało zrealizowane poprzez tablicę zmiennych rzeczywistych (LREAL). W momencie odczytu wejścia wartość wpisywana jest w poprzednie miejsce w tablicy. Po odczycie zwiększany jest indeks tablicy, a w przypadku przekroczenia zakresu pobierana jest pierwsza wartość z tablicy. Na koniec następuje wyliczenie wartości wyjścia obiektu z równania dyskretnego. W równaniu czas próbkowania jest taki sam czas wywołania programu sterownika ( w moim teście 20 ms).

Podsumowanie

Tak zrealizowany regulator oraz model obiektu pozwolił wykonać badania metod samo-strojenia regulatora PID. Pokazuje to, że suchą teorię i symulacje wykonywane na studiach można z powodzeniem wykorzystać w symulatorze oraz rzeczywistym sterowniku PLC.