Wikipedia pisze:

„Do końca lat sześćdziesiątych XX wieku praktycznie wszystkie układy sterowania maszyn i urządzeń, zarówno wykonywane w tradycyjnej technice przekaźnikowo-stycznikowej jak i w technice półprzewodnikowej, były konstruowane jako sztywna sieć logiczna. Rolę programu spełniało okablowanie pomiędzy stycznikami, przekaźnikami oraz innymi elementami specjalnymi.”

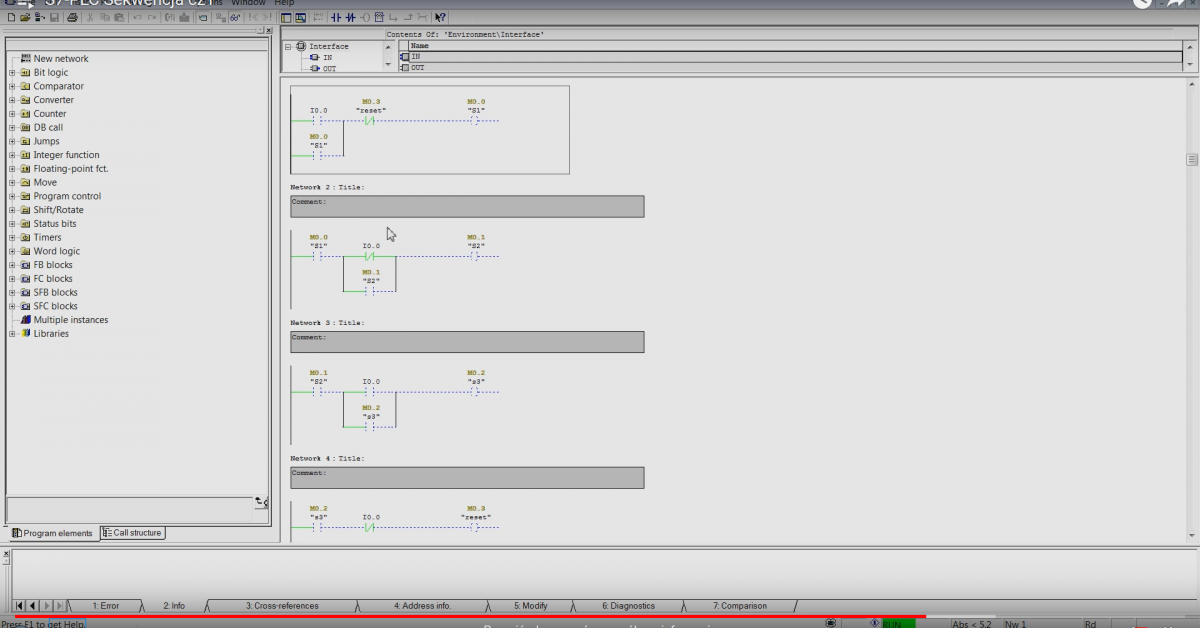

Więc w tym artykule zrobię to samo. Trochę powrót do przeszłości. W pierwszej części kursu programowania PLC zaprezentowałem metodę pisania sekwencji w sterowniku PLC z wykorzystanie języka LAD

Język „LD” wzoruje się na schematach przekaźnikowych, jednak w odróżnieniu od układów przekaźnikowych jest programem. Dziś jednak nie trzeba kabli i przekaźników i by zrobić układ logiczny. Rozwianiem jest układ FPGA (programowalne układy logiczne).

Różnica między mikro-kontrolerem a układem FPGA jest taka, że do mikro-kontrolera wgrywamy program a do układu FPGA konfigurację. Z układu FPGA poprzez wgranie odpowiedniej konfiguracji możemy zrobić mikro-kontroler.

Szczegóły techniczne

Spora większość moich kursów opiera się w zasadzie na jednym temacie „Załącz – Wyłacz” jednym przyciskiem. Więc i tu co by uszanować tradycję zrobię to samo. Układ przedstawiony poniżej będzie dokładną kopią mojego tutoriala z przed kilku lat (Ten z linku na górze), z tą różnicą że teraz to nie będzie program a konfiguracja układu FPGA.

- Środowisko Intel Quartus 18.1 FPGA altera MAX10 .

- To będzie symulacja. Układ rzeczywisty wymagał by filtrowania wejść ze względu na drgania styków.

- Układ będzie kopią programu „LD” ze zdjęcia poniżej.

Patrząc na pierwszy network z góry, układ „seta” z potrzymaniem wygląda następująco:

- S1= (I0.0 OR S1) and not Reset;

Co w przeniesieniu na język opisu sprzętu verilog będzie wyglądało następująco:

- assign state[0]=(pb|state[0])&~state[3];

Gdzie „I0.0” to w przekładzie „PB” (pushButton), a „S1” to „state[0]” w rozumieniu to krok pierwszy. „Reset” zaś to „state[3]”.

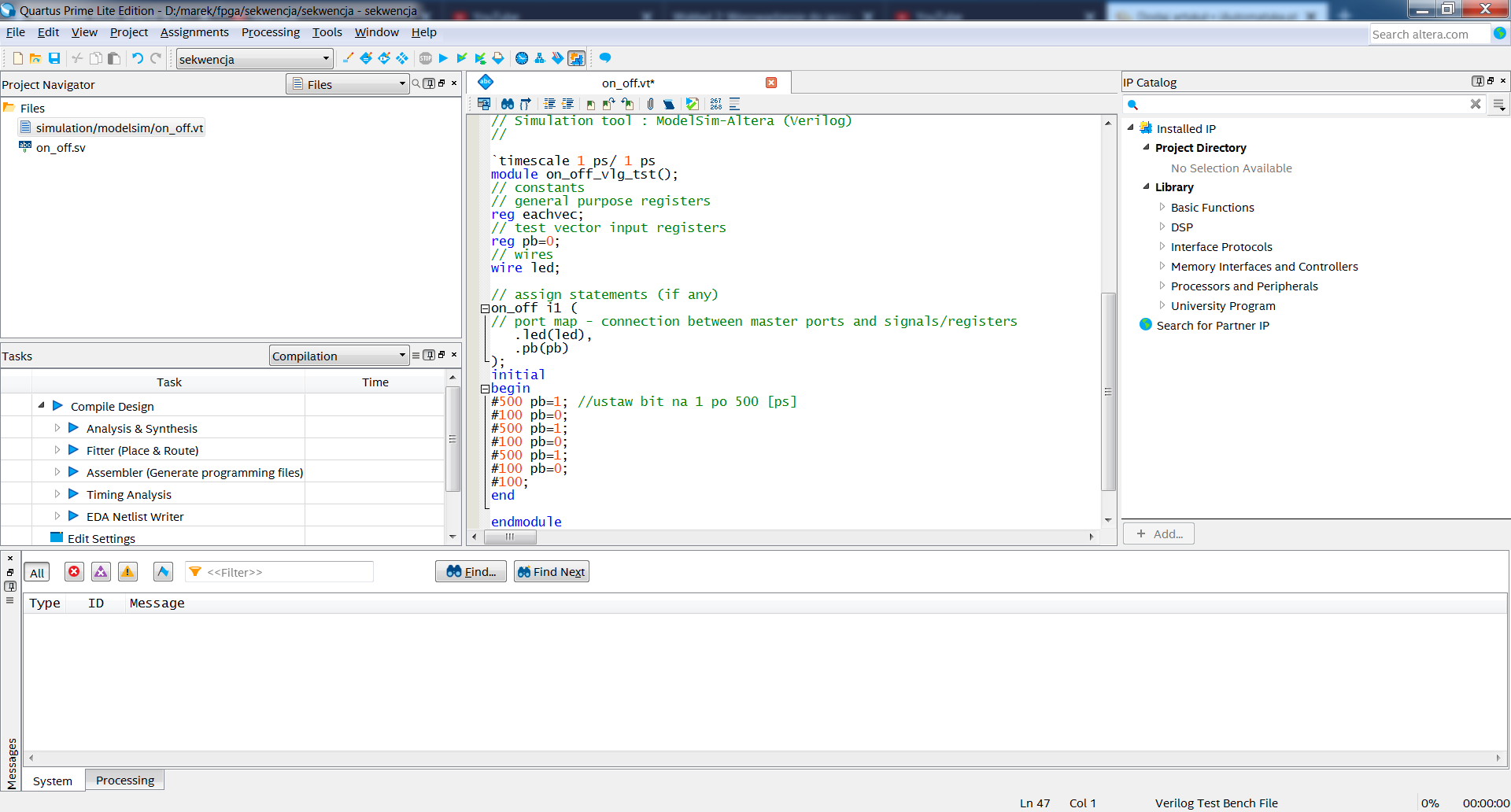

Kompletna konfiguracja w języku verilog wygląda tak:

Tak opisany układ logiczny możemy zasymulować. W tym celu można napisać prosty test bench z wymuszeniami a następne przeprowadzić symulację by uzyskać odpowiedź układu.

W pliku test bench właściwie jako wymuszenie zmieniam tyklo stan bitu „pb” – pusButton

Wynik symulacji tego układu logicznego:

Na koniec jeszcze ta sama sekwencja napisana troszkę w innym stylu. Do zaimplementowania w układzie FPGA.

Podsumowanie

Krótki artykuł o budowaniu układów logicznych (jak w czasach przed upowszechnieniem sterowników PLC), ale z wykorzystaniem technologii FPGA. Może kogoś zaciekawi takie podejście do sprawy. A czy konfigurowalna logika wygra z programem? Zaletami jest szybkość działania, wadą zaś ograniczenie zasobów i cena.

Artykuł został nagrodzony w Konkursie iAutomatyka – edycja Grudzień 2019 Artykuł został nagrodzony w Konkursie iAutomatyka – edycja Grudzień 2019

Nagrodę Bidon + zestaw SKINTOP + zestaw gadżetów dostarcza ambasador konkursu, firma LAPP. |